ラッチは、信号レベル(信号遷移ではなく)で動作する基本的な記憶素子である。 クロック遷移で制御されるラッチはフリップフロップです。 ラッチはレベル感応型デバイスです。 ラッチは非同期順序回路の設計に有用である。

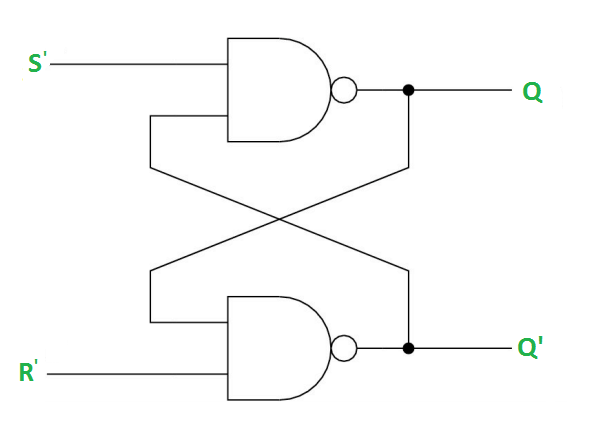

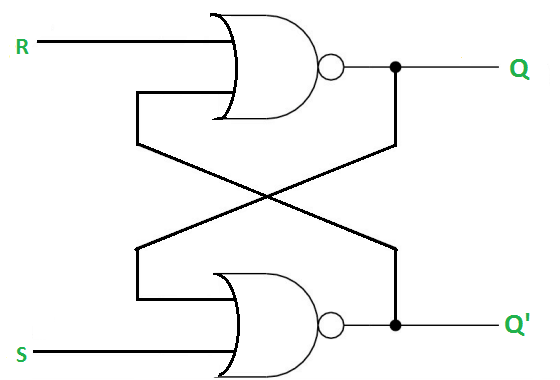

SR(セット・リセット)ラッチ – SRラッチは、

(i)2つのクロスカップリングNORゲートまたは2つのクロスカップリングNANDゲート、

(ii)2入力SETとRESET、

(iii)2出力Q、Q’からなる回路である。

| q | q’ | state |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

正常な状態であること。 入力はともに0のままです。 以下は、NANDゲートを使ったRSラッチです。

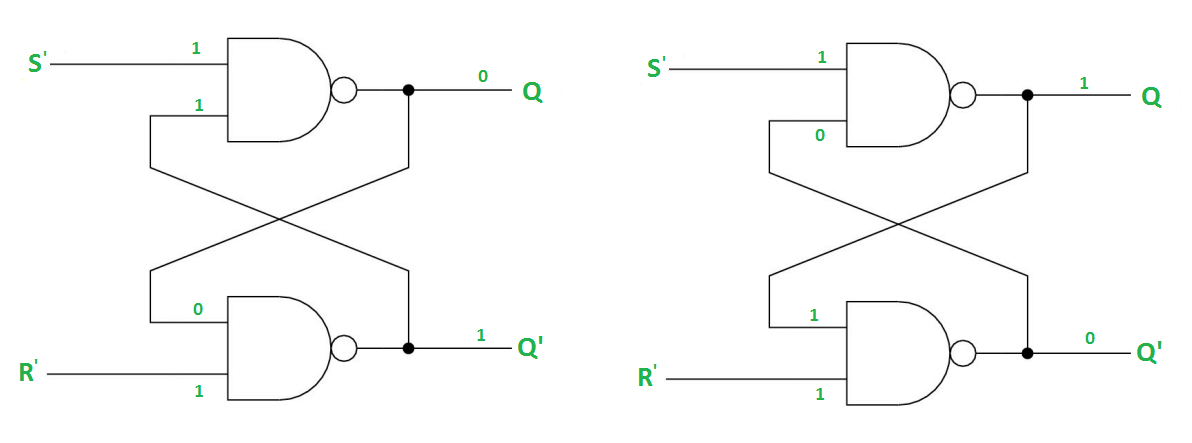

ケース-1: S’=R’=1 (S=R=0) –

Q=1なら、2番目のNANDゲートのQとR’はともに1です。

Case-2: S’=0, R’=1 (S=1, R=0) –

S’=0なので、1番目のNANDゲートの出力、Q=1(セット状態)です。 2番目のNANDゲートでは、QとR’の入力が1なので、Q’=0となる。

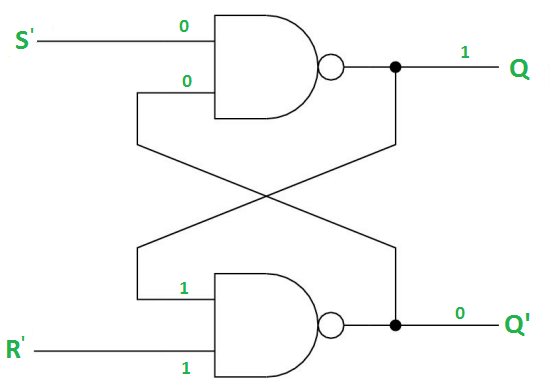

Case-3: S’=1, R’=0 (S=0, R=1) –

R’=0 なので2番目のNANDゲート、Q’=1 の出力になる。

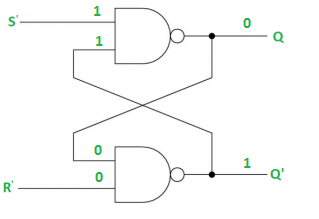

Case-4: S’= R’= 0 (S=R=1) –

S=R=1のとき、QとQ’は共に1になり、これは許されないことである。 したがって、この入力条件は禁止されています。

NORゲートを使ったSRラッチを以下に示します。

ゲーテッドSRラッチ –

ゲーテッドSRラッチとはイネーブル入力のSRラッチでイネーブル=1時に動作しイネーブル=0時に前の状態を保持するものです。

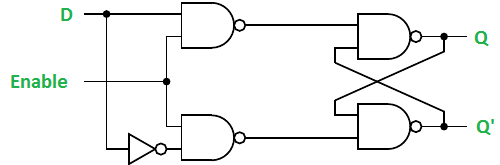

Gated D Latch –

Dラッチは、SRラッチと似ていますが、いくつかの変更が加えられています。 ここでは、入力は互いに補い合うものです。 イネーブル信号を使用したDラッチの設計を以下に示します:

Dラッチの真理値表を以下に示します。

| イネーブル | D | Q(n) | Q(n+1) | State | ||

|---|---|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET | x | 1 | SET |

| 0 | x | 1 | 1 | 1 | 1 | 0 | 1x | Q(n) | No Change |

入力Dと同じ出力となるため、出力は同じ。 Dラッチは、トランスペアレントラッチとも呼ばれます。 真理値表を考慮すると、イネーブル入力のあるDラッチの特性式は次のようになります: