Západky jsou základní paměťové prvky, které pracují s úrovněmi signálů (nikoli s jejich přechody). Západky řízené hodinovým přechodem jsou flip-flopy. Západky jsou zařízení citlivá na úroveň. Latche jsou užitečné pro návrh asynchronního sekvenčního obvodu.

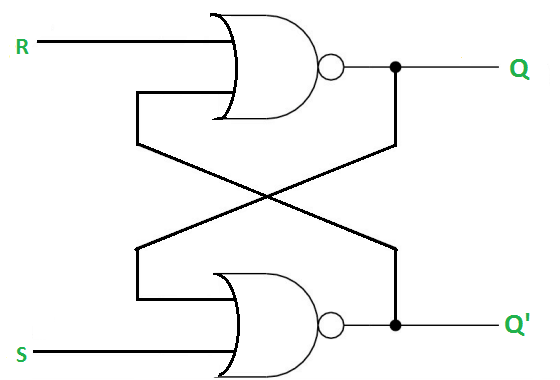

SR (Set-Reset) Latch – SR Latch je obvod s:

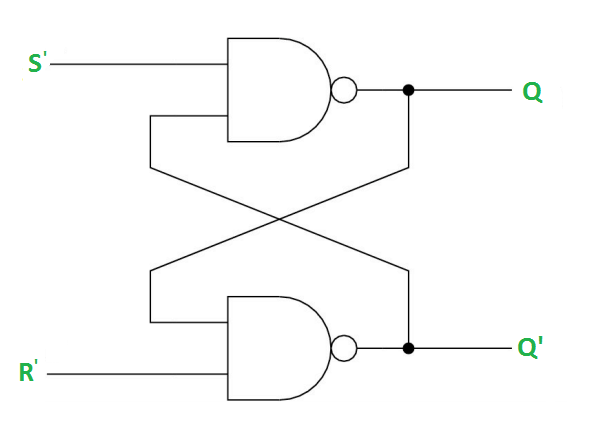

(i) 2 křížově spojenými hradly NOR nebo 2 křížově spojenými hradly NAND.

(ii) 2 vstupy S pro SET a R pro RESET.

(iii) 2 výstupy Q, Q‘.

| Q | Q‘ | STATE |

|---|---|---|

| 1 | 0 | Nastavit |

| 0 | 1 | Reset |

Při normálních podmínkách, oba vstupy zůstávají na hodnotě 0. Následuje RS Latch s hradly NAND:

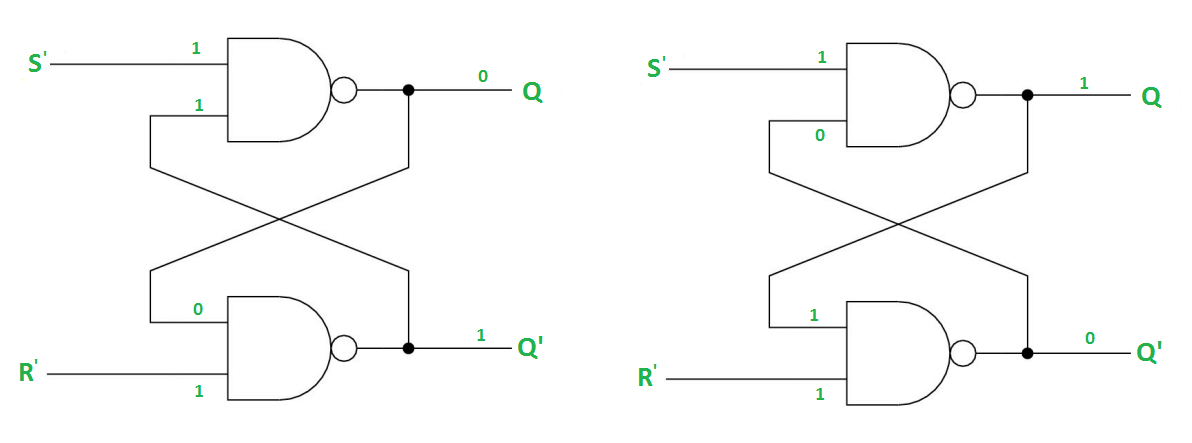

Případ-1: S’=R’=1 (S=R=0) –

Pokud je Q = 1, vstupy Q a R‘ pro 2. hradlo NAND jsou oba 1.

Jestliže Q = 0, vstupy Q a R‘ pro 2. hradlo NAND jsou 0 a 1.

Případ-2: S’=0, R’=1 (S=1, R=0) –

Jestliže S’=0, výstup 1. hradla NAND, Q = 1(stav SET). Ve 2. hradle NAND, protože vstupy Q a R‘ jsou 1, Q’=0.

Případ-3: S’= 1, R’= 0 (S=0, R=1) –

Jakože R’=0, výstup 2. hradla NAND, Q‘ = 1. Protože v 1. hradle NAND jsou vstupy Q a S‘ 1, Q=0(stav RESET).

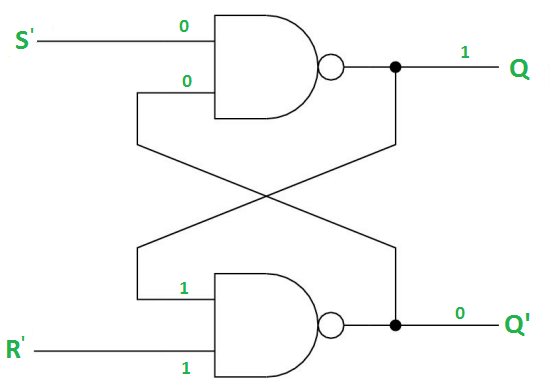

Případ-4: S’= R’= 0 (S=R=1) –

Když S=R=1, Q i Q‘ se stanou 1, což není dovoleno. Vstupní podmínka je tedy zakázána.

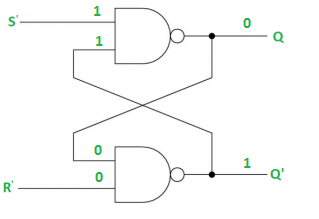

Západka SR s použitím hradla NOR je znázorněna níže:

Západka SR se zapínáním –

Západka SR se zapínáním je západka SR s povolovacím vstupem, která pracuje, když je povoleno 1, a zachovává předchozí stav, když je povoleno 0.

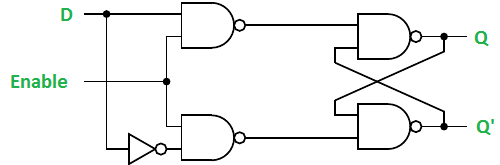

Gated D Latch –

D latch je podobný SR latch s některými provedenými úpravami. Vstupy jsou zde vzájemně komplementární. Návrh D-západky se signálem Enable je uveden níže:

Pravdivostní tabulka pro D-západku je uvedena níže:

| Enable | D | Q(n) | Q(n+1) | STATE |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | bez změny |

Jako výstup je stejný jako vstup D, D západka se také nazývá transparentní západka. S ohledem na pravdivostní tabulku lze charakteristickou rovnici pro D západku s povoleným vstupem zadat takto:

Q(n+1) = EN.D + EN'.Q(n)