Latches er grundlæggende lagringselementer, der fungerer med signalniveauer (i stedet for signalovergange). Latches, der styres af en clockovergang, er flip-flops. Latches er niveaufølsomme enheder. Latches er nyttige til design af det asynkrone sekventielle kredsløb.

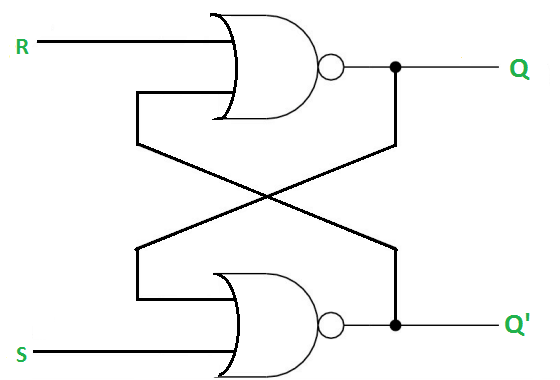

SR (Set-Reset) Latch – SR Latch er et kredsløb med:

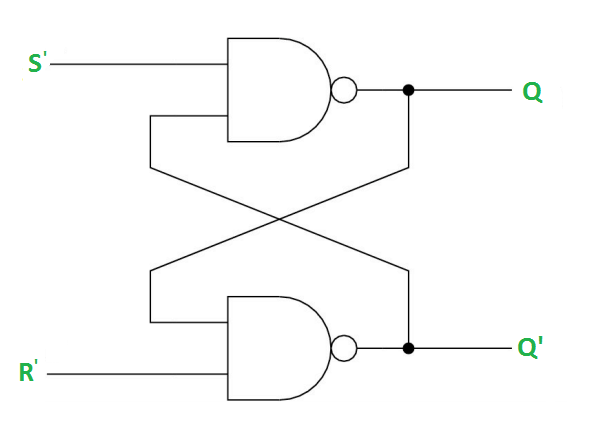

(i) 2 krydskoblede NOR-gate eller 2 krydskoblede NAND-gate.

(ii) 2 indgange S for SET og R for RESET.

(iii) 2 udgange Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

Under normale forhold, forbliver begge indgange 0. Følgende er RS Latch med NAND-gates:

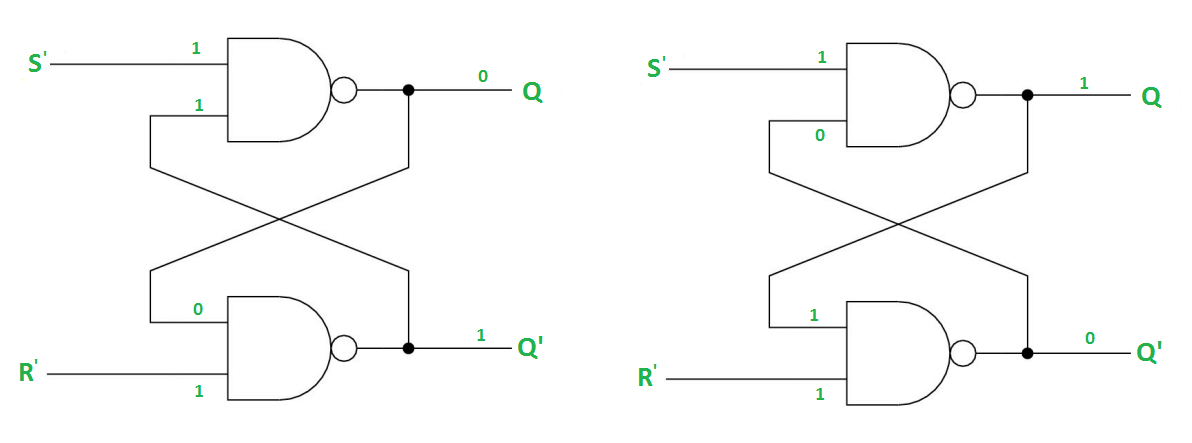

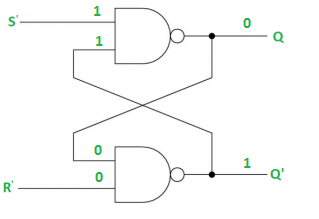

Fald-1: S’=R’=1 (S=R=0) –

Hvis Q = 1, er Q- og R’-indgangene for 2. NAND-gate begge 1.

Hvis Q = 0, er Q- og R’-indgangene for 2. NAND-gate henholdsvis 0 og 1.

Case-2: S’=0, R’=1 (S=1, R=0) –

Som S’=0, er udgangen af 1. NAND-gate, Q = 1(SET-tilstand). I 2. NAND-gate, da Q og R’-indgangene er 1, er Q’=0.

Fælde-3: S’= 1, R’= 0 (S=0, R=1) –

Som R’=0, er udgangen af 2. NAND-gate, Q’ = 1. I 1. NAND-gate, da Q og S’ indgangene er 1, bliver Q=0 (RESET-tilstand).

Fælde-4: S’= R’= 0 (S=R=1) –

Når S=R=1, bliver både Q og Q’ 1, hvilket ikke er tilladt. Så indgangsbetingelsen er forbudt.

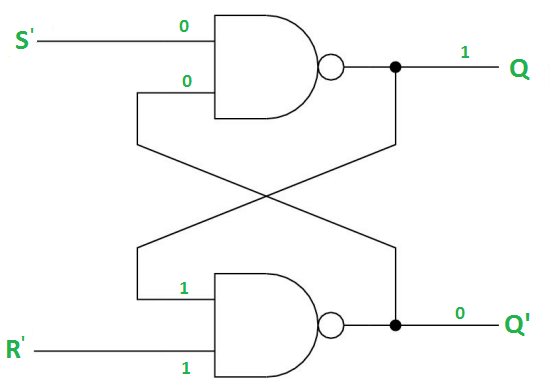

SR-latch med NOR-gate er vist nedenfor:

Gated SR Latch –

En Gated SR latch er en SR latch med enable-indgang, som fungerer, når enable er 1 og bevarer den tidligere tilstand, når enable er 0.

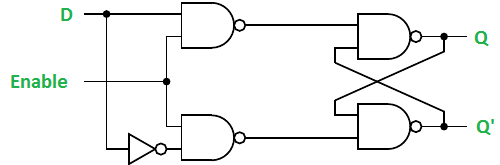

Gated D Latch –

D latch ligner SR latch med nogle ændringer. Her er indgangene komplementer til hinanden. Designet af D-Latch med Enable-signal er angivet nedenfor:

Sandhedstabellen for D-Latch er vist nedenfor:

| Enable | D | Q(n) | Q(n+1) | STATE | |

|---|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET | |

| 1 | 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | Ingen ændring |

Som output er det samme som input D, D latch kaldes også for Transparent Latch. I betragtning af sandhedstabellen kan den karakteristiske ligning for D latch med enable-indgang angives som:

Q(n+1) = EN.D + EN'.Q(n)