Zatrzaski są podstawowymi elementami pamięci, które działają z poziomami sygnałów (a nie z przejściami sygnałów). Zatrzaski sterowane przejściem zegarowym to flip-flops. Zatrzaski są urządzeniami wrażliwymi na poziom. Zatrzaski są użyteczne przy projektowaniu asynchronicznego obwodu sekwencyjnego.

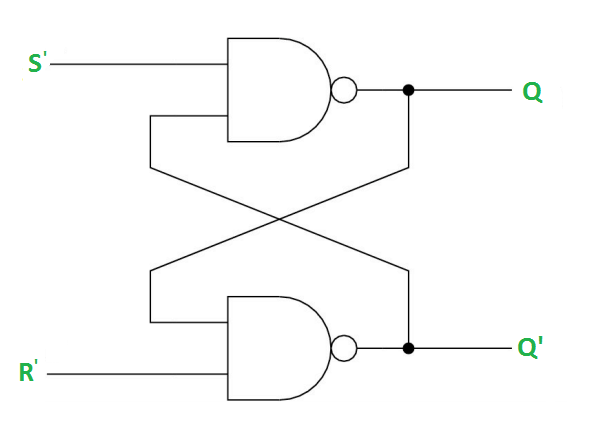

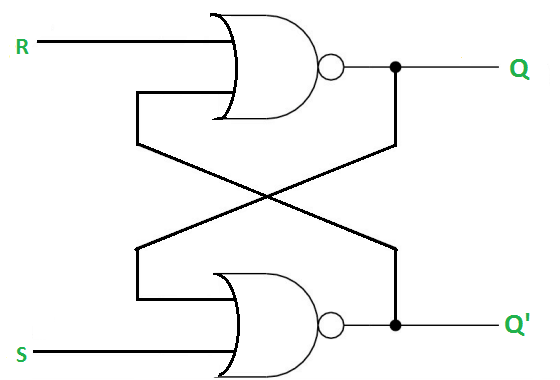

SR (Set-Reset) Latch – SR Latch jest układem z:

(i) 2 poprzecznie sprzężonymi bramkami NOR lub 2 poprzecznie sprzężonymi bramkami NAND.

(ii) 2 wejściami S dla SET i R dla RESET.

(iii) 2 wyjściami Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

W normalnych warunkach, oba wejścia pozostają 0. Poniżej przedstawiony jest układ RS Latch z bramkami NAND:

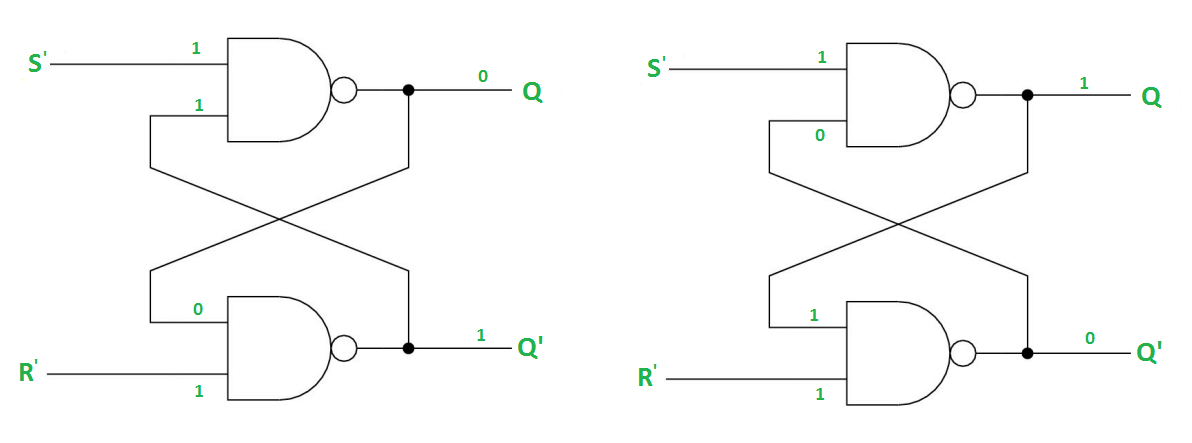

Case-1: S’=R’=1 (S=R=0) –

Jeśli Q = 1, wejścia Q i R’ dla drugiej bramki NAND są po 1.

Jeśli Q = 0, wejścia Q i R’ dla 2. bramki NAND są odpowiednio 0 i 1.

Case-2: S’=0, R’=1 (S=1, R=0) –

Jak S’=0, wyjście 1. bramki NAND, Q = 1(stan SET). W 2. bramce NAND, ponieważ wejścia Q i R’ są 1, Q’=0.

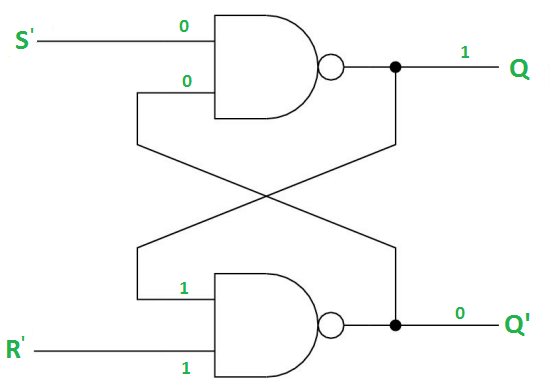

Case-3: S’= 1, R’= 0 (S=0, R=1) –

As R’=0, the output of 2nd NAND gate, Q’ = 1. W 1. bramce NAND, ponieważ wejścia Q i S’ są 1, Q=0(stan RESET).

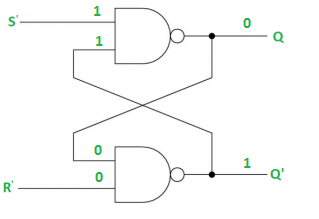

Case-4: S’= R’= 0 (S=R=1) –

Gdy S=R=1, zarówno Q jak i Q’ stają się 1, co jest niedozwolone. Tak więc, warunek wejścia jest zabroniony.

Zatrzask SR wykorzystujący bramkę NOR jest pokazany poniżej:

Zatrzask SR bramkowany –

Zatrzask SR bramkowany jest zatrzaskiem SR z wejściem enable, który działa, gdy enable jest 1 i zachowuje poprzedni stan, gdy enable jest 0.

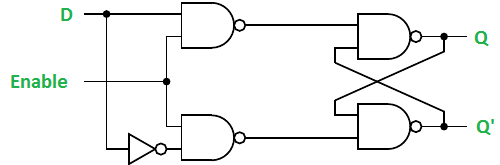

Zatrzymanie D –

Zatrzymanie D jest podobne do zatrzasku SR z pewnymi modyfikacjami. Tutaj wejścia są komplementarne względem siebie. Projekt zatrzasku D z sygnałem Enable jest podany poniżej:

Tablica prawdy dla zatrzasku D jest pokazana poniżej:

| Enable | D | Q(n) | Q(n+1) | STATE | |

|---|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET | |

| 1 | 1 | x | 1 | SET | |

| 0 | x | x | x | Q(n) | No Change |

As the output is the same as the input D, D zatrzask jest również nazywany zatrzaskiem przezroczystym. Biorąc pod uwagę tabelę prawdy, równanie charakterystyczne dla zatrzasku D z wejściem zezwalającym może być podane jako:

Q(n+1) = EN.D + EN'.Q(n)

.