Latches sunt elemente de stocare de bază care operează cu niveluri de semnal (mai degrabă decât cu tranziții de semnal). Zăbrelele controlate de o tranziție de ceas sunt flip-flops. Zăbrelele sunt dispozitive sensibile la nivel. Latch-urile sunt utile pentru proiectarea circuitului secvențial asincron.

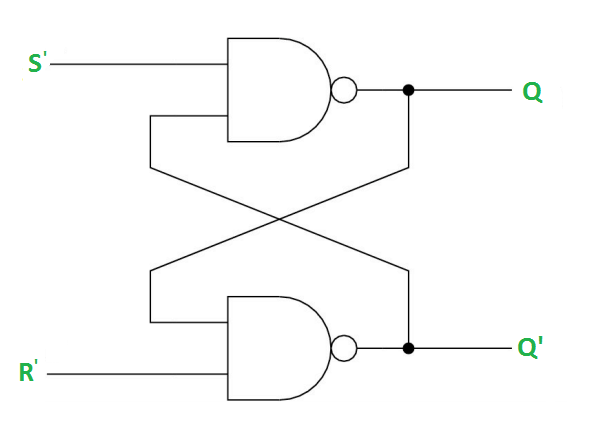

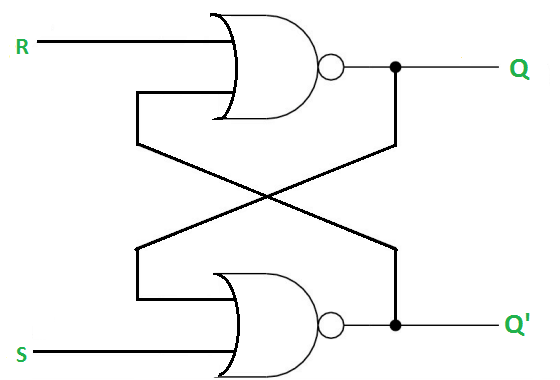

SR (Set-Reset) Latch – SR Latch este un circuit cu:

(i) 2 porți NOR cuplate încrucișat sau 2 porți NAND cuplate încrucișat.

(ii) 2 intrări S pentru SET și R pentru RESET.

(iii) 2 ieșiri Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

În condiții normale, ambele intrări rămân 0. În cele ce urmează se prezintă RS Latch cu porți NAND:

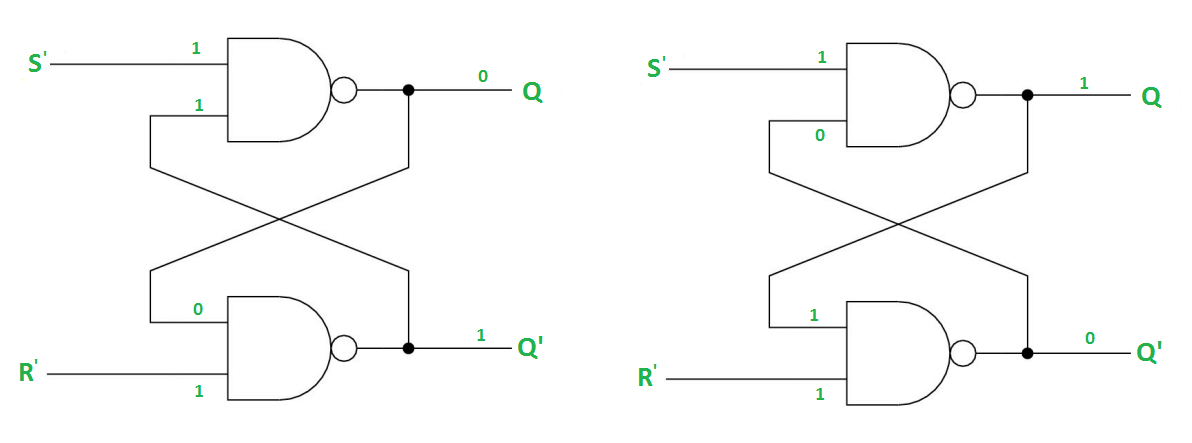

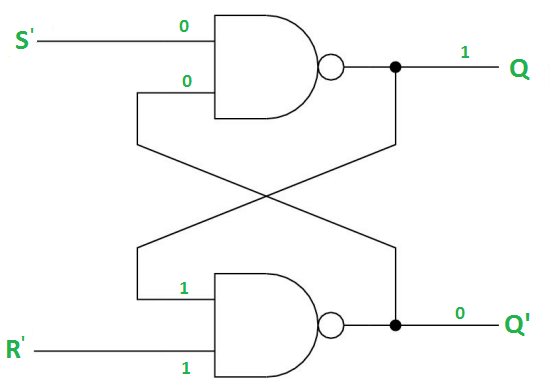

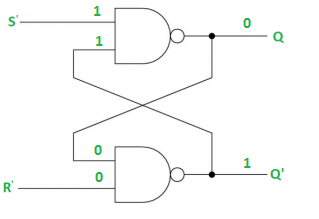

Cazul-1: S’=R’=1 (S=R=0) –

Dacă Q = 1, intrările Q și R’ pentru a doua poartă NAND sunt ambele 1.

Dacă Q = 0, intrările Q și R’ pentru a 2-a poartă NAND sunt 0 și, respectiv, 1.

Cazul-2: S’=0, R’=1 (S=1, R=0) –

Dacă S’=0, ieșirea primei porți NAND, Q = 1 (starea SET). În cea de-a 2-a poartă NAND, deoarece intrările Q și R’ sunt 1, Q’=0.

Cazul-3: S’= 1, R’= 0 (S=0, R=1) –

Cum R’=0, la ieșirea celei de-a 2-a porți NAND, Q’ = 1. În prima poartă NAND, deoarece intrările Q și S’ sunt 1, Q=0 (starea RESET).

Cazul-4: S’= R’= 0 (S=R=1) –

Când S=R=1, atât Q cât și Q’ devin 1, ceea ce nu este permis. Așadar, condiția de intrare este interzisă.

Latch-ul SR Latch folosind poarta NOR este prezentat mai jos:

Gated SR Latch –

Un Gated SR latch este un SR latch cu intrare de activare care funcționează când activarea este 1 și păstrează starea anterioară când activarea este 0.

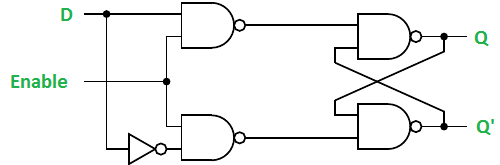

Gated D Latch –

D latch este similar cu SR latch cu unele modificări aduse. Aici, intrările sunt complemente una față de cealaltă. Proiectarea latch-ului D cu semnal de activare este prezentată mai jos:

Tabelul de adevăr pentru D-Latch este prezentat mai jos:

| Enable | D | Q(n) | Q(n+1) | STATE | |

|---|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET | |

| 1 | 1 | x | 1 | SET | |

| 0 | 0 | x | x | Q(n) | Nici o schimbare |

Ca urmare a faptului că ieșirea este aceeași cu intrarea D, D latch se mai numește și latch transparent. Având în vedere tabelul de adevăr, ecuația caracteristică pentru D latch cu intrare de activare poate fi dată sub forma:

Q(n+1) = EN.D + EN'.Q(n)

.