Los Latches son elementos básicos de almacenamiento que operan con niveles de señal (en lugar de transiciones de señal). Los latches controlados por una transición de reloj son flip-flops. Los latches son dispositivos sensibles al nivel. Los latches son útiles para el diseño del circuito secuencial asíncrono.

Latch SR (Set-Reset) – El Latch SR es un circuito con:

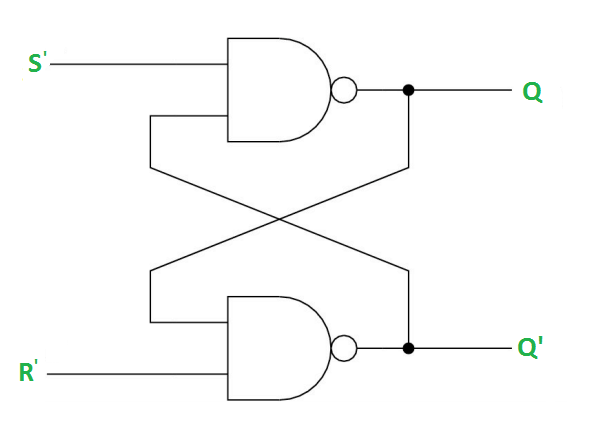

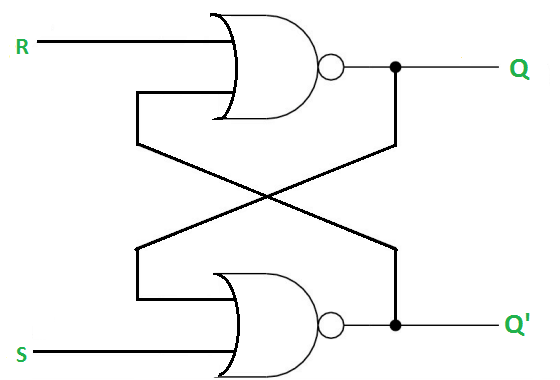

(i) 2 puertas NOR acopladas en cruz o 2 puertas NAND acopladas en cruz.

(ii) 2 entradas S para SET y R para RESET.

(iii) 2 salidas Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

En condiciones normales, ambas entradas permanecen en 0. El siguiente es el RS Latch con puertas NAND:

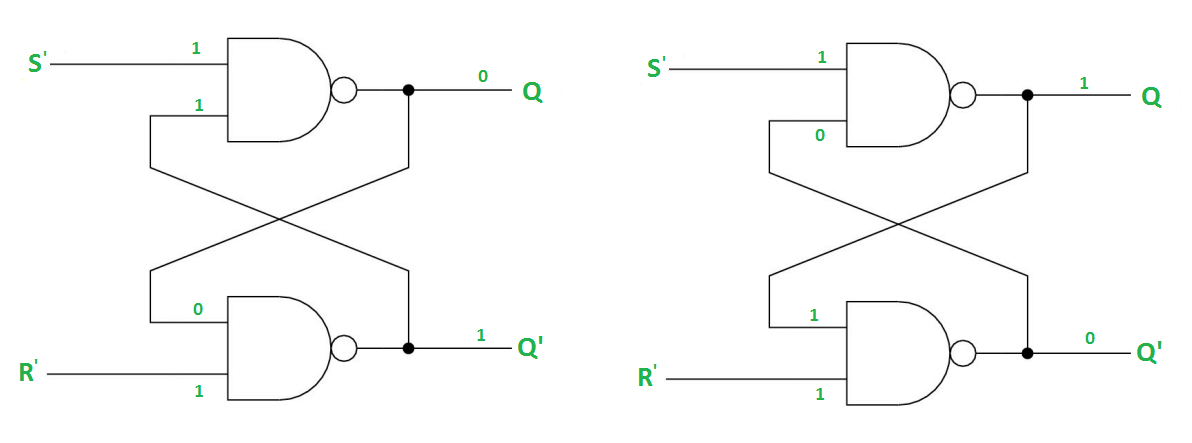

Caso-1: S’=R’=1 (S=R=0) –

Si Q = 1, las entradas Q y R’ de la 2ª puerta NAND son ambas 1.

Si Q = 0, las entradas Q y R’ de la 2ª puerta NAND son 0 y 1 respectivamente.

Caso-2: S’=0, R’=1 (S=1, R=0) –

Como S’=0, la salida de la 1ª puerta NAND, Q = 1(estado SET). En la 2ª puerta NAND, como las entradas Q y R’ son 1, Q’=0.

Caso 3: S’= 1, R’= 0 (S=0, R=1) –

Como R’=0, la salida de la 2ª puerta NAND, Q’ = 1. En la 1ª puerta NAND, como las entradas Q y S’ son 1, Q=0(estado RESET).

Caso 4: S’= R’= 0 (S=R=1) –

Cuando S=R=1, tanto Q como Q’ se convierten en 1 lo cual no está permitido. Por lo tanto, la condición de entrada está prohibida.

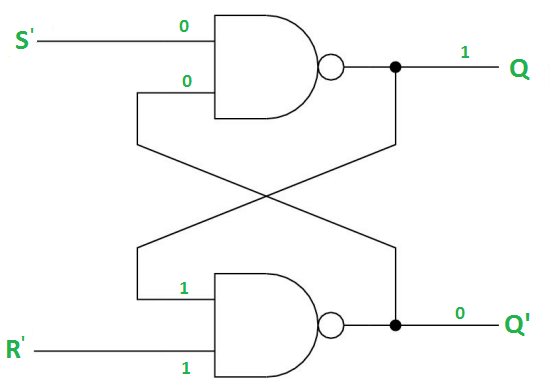

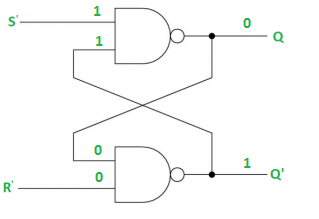

El SR Latch utilizando la puerta NOR se muestra a continuación:

Gated SR Latch –

Un Gated SR latch es un SR latch con entrada de habilitación que funciona cuando la habilitación es 1 y retiene el estado anterior cuando la habilitación es 0.

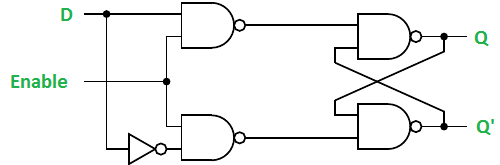

Gated D Latch –

D latch es similar al SR latch con algunas modificaciones. En este caso, las entradas son complementarias entre sí. El diseño del D latch con la señal Enable se da a continuación:

La tabla de verdad para el D-Latch se muestra a continuación:

| Habilitar | D | Q(n) | Q(n+1) | Estado |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | Sin Cambio |

Como la salida es igual a la entrada D, El latch D también se llama Latch Transparente. Considerando la tabla de verdad, la ecuación característica para el latch D con entrada de habilitación puede ser dada como:

Q(n+1) = EN.D + EN'.Q(n)