Latcher är grundläggande lagringselement som arbetar med signalnivåer (snarare än signalövergångar). Latcher som styrs av en klockövergång är flip-flops. Latcher är nivåkänsliga enheter. Latches är användbara för utformningen av den asynkrona sekventiella kretsen.

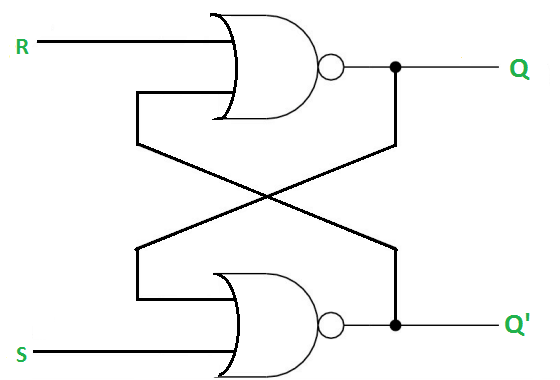

SR (Set-Reset) Latch – SR Latch är en krets med:

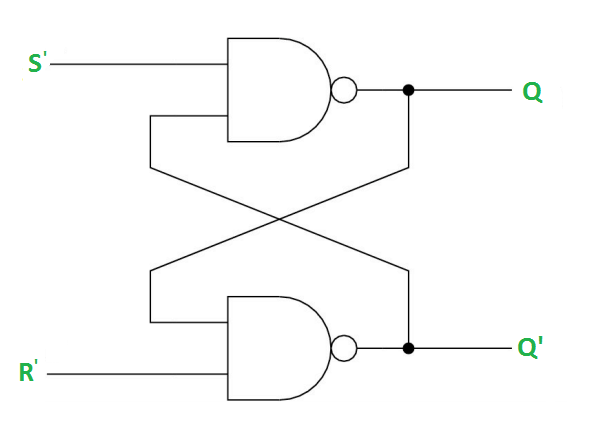

(i) 2 korskopplade NOR-portar eller 2 korskopplade NAND-portar.

(ii) 2 ingångar S för SET och R för RESET.

(iii) 2 utgångar Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

Under normala förhållanden, förblir båda ingångarna 0. Följande är RS Latch med NAND-gates:

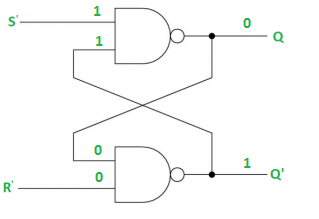

Fall-1: S’=R’=1 (S=R=0) –

Om Q = 1 är Q och R’-ingångarna för den andra NAND-gaten båda 1.

Om Q = 0 är Q- och R-ingångarna för den andra NAND-porten 0 respektive 1.

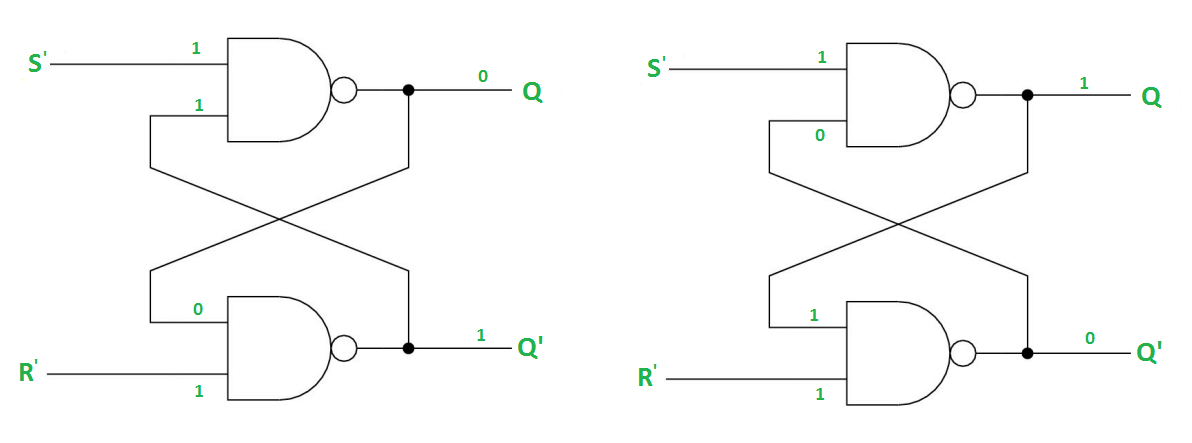

Fall-2: S’=0, R’=1 (S=1, R=0) –

Som S’=0 är utgången från den första NAND-porten, Q = 1 (SET-tillstånd). I den andra NAND-porten, eftersom Q och R’ ingångarna är 1, är Q’=0.

Fall-3: S’= 1, R’= 0 (S=0, R=1) –

Att R’=0 är utgångspunkten för den andra NAND-porten, Q’ = 1. I den första NAND-porten är Q och S’ ingångarna 1, Q=0 (RESET-tillstånd).

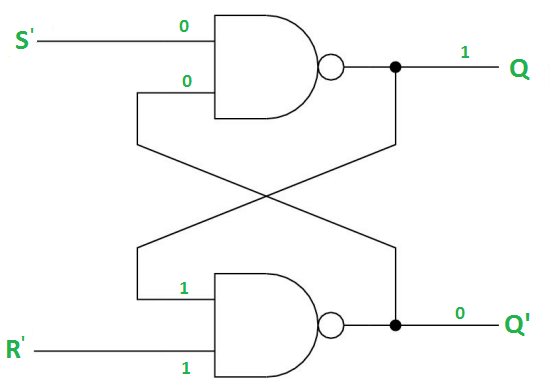

Fall-4: S’= R’= 0 (S=R=1) –

När S=R=1 blir både Q och Q’ 1, vilket inte är tillåtet. Ingångsvillkoret är alltså förbjudet.

S SR Latch med NOR-gate visas nedan:

Gated SR Latch –

En Gated SR Latch är en SR Latch med aktiveringsingång som fungerar när aktiveringen är 1 och behåller det tidigare tillståndet när aktiveringen är 0.

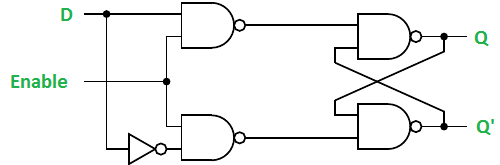

Gated D Latch –

D Latch liknar SR Latch med vissa ändringar. Här är ingångarna komplement till varandra. Utformningen av D-latch med Enable-signal ges nedan:

Sanningstabellen för D-latch visas nedan:

| Enable | D | Q(n) | Q(n+1) | STATE | |

|---|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET | |

| 1 | 1 | x | 1 | SET | |

| 0 | x | x | Q(n) | Ingen förändring |

Som utgång är samma som ingång D, D latch kallas också för Transparent Latch. Med hänsyn till sanningstabellen kan den karakteristiska ekvationen för D latch med aktiveringsingång ges som:

Q(n+1) = EN.D + EN'.Q(n)