A reteszek olyan alapvető tárolóelemek, amelyek jelszintekkel (és nem jelátmenetekkel) működnek. Az órajelátmenettel vezérelt reteszek flip-flopok. A reteszek szintérzékeny eszközök. A reteszek hasznosak az aszinkron szekvenciális áramkörök tervezésénél.

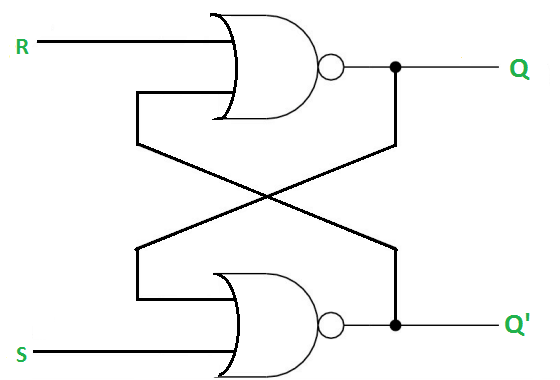

SR (Set-Reset) retesz – Az SR retesz olyan áramkör, amely rendelkezik:

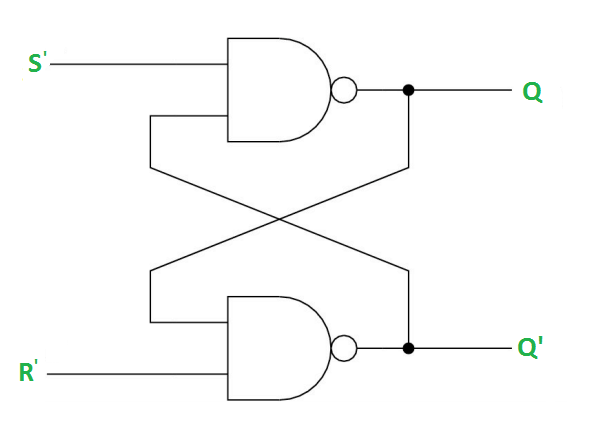

(i) 2 keresztbe kapcsolt NOR kapuval vagy 2 keresztbe kapcsolt NAND kapuval.

(ii) 2 bemenet S a SET és R a RESET számára.

(iii) 2 kimenet Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

Normális körülmények között, mindkét bemenet 0 marad. A következő az RS Latch NAND-kapukkal:

1. eset: S’=R’=1 (S=R=0) –

Ha Q = 1, akkor a 2. NAND-kapu Q és R’ bemenete egyaránt 1.

Ha Q = 0, a 2. NAND-kapu Q és R’ bemenete 0, illetve 1.

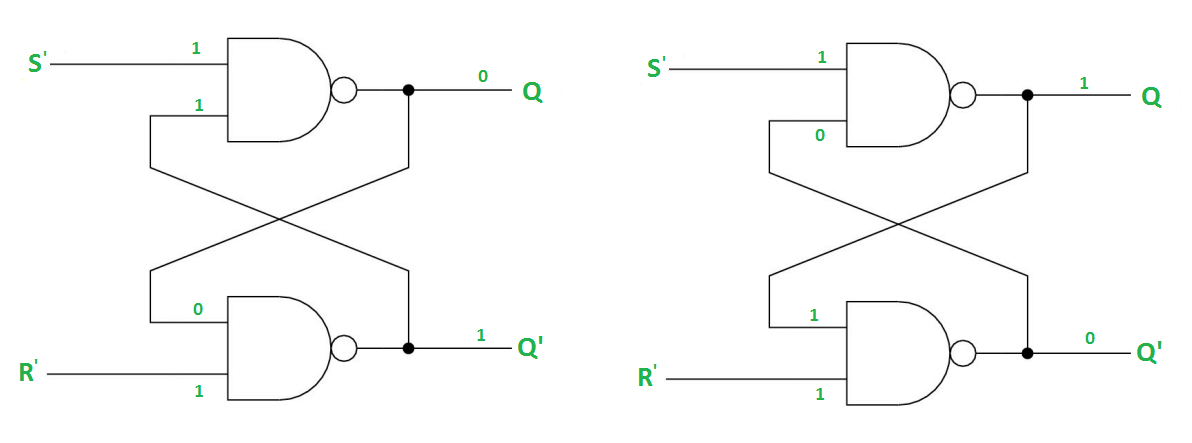

2. eset: S’=0, R’=1 (S=1, R=0) –

Mivel S’=0, az 1. NAND-kapu kimenete, Q = 1 (SET állapot). A 2. NAND-kapuban, mivel Q és R’ bemenete 1, Q’=0.

3. eset: S’=1, R’=0 (S=0, R=1) –

Mivel R’=0, a 2. NAND-kapu kimenete Q’ = 1. Az 1. NAND-kapuban, mivel Q és S’ bemenete 1, Q=0 (RESET állapot).

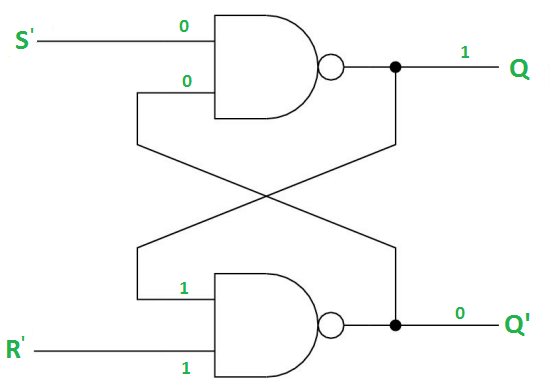

4. eset: S’= R’= 0 (S=R=1) –

Ha S=R=1, Q és Q’ is 1 lesz, ami nem megengedett. Tehát a bemeneti feltétel tiltott.

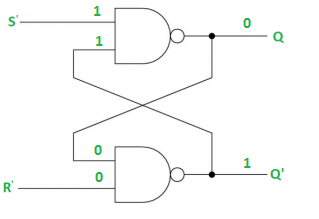

A NOR-kaput használó SR retesz az alábbiakban látható:

Gated SR Latch –

A Gated SR latch egy olyan SR retesz engedélyező bemenettel, amely akkor működik, ha az engedélyezés 1, és megtartja az előző állapotot, ha az engedélyezés 0.

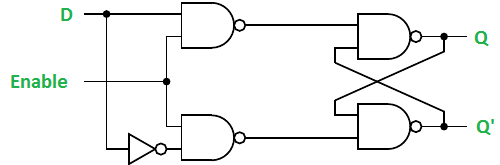

Gated D Latch –

A D retesz hasonló az SR reteszhez, néhány módosítással. Itt a bemenetek egymás komplementerei. A D-retesz tervezése Enable jellel az alábbiakban látható:

A D-retesz igazságtáblázata az alábbiakban látható:

| Enable | D | Q(n) | Q(n+1) | STATE |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | No Change |

Mivel a kimenet megegyezik a bemeneti D-vel, A D reteszt transzparens retesznek is nevezik. Az igazságtáblázatot figyelembe véve a D retesz jellemző egyenlete engedélyező bemenettel a következőképpen adható meg:

Q(n+1) = EN.D + EN'.Q(n)