I latches sono elementi di memoria di base che operano con livelli di segnale (piuttosto che con transizioni di segnale). Le chiusure controllate da una transizione di clock sono flip-flop. I latches sono dispositivi sensibili al livello. I latches sono utili per la progettazione del circuito sequenziale asincrono.

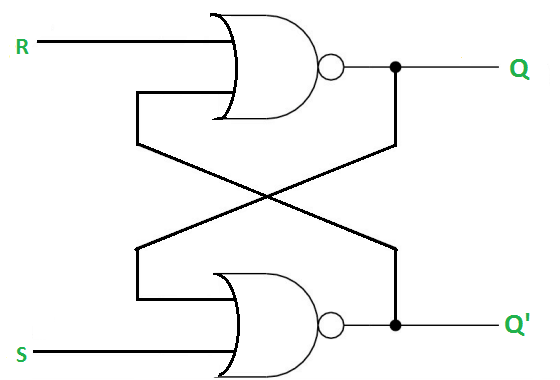

SR (Set-Reset) Latch – SR Latch è un circuito con:

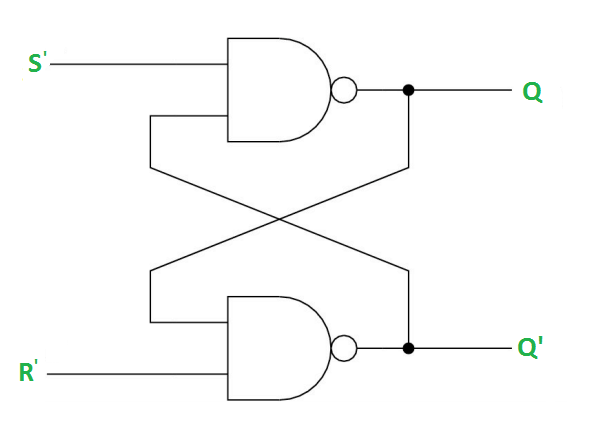

(i) 2 porte NOR accoppiate incrociate o 2 porte NAND accoppiate incrociate.

(ii) 2 ingressi S per SET e R per RESET.

(iii) 2 uscite Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

In condizioni normali, entrambi gli ingressi rimangono 0. Il seguente è l’RS Latch con porte NAND:

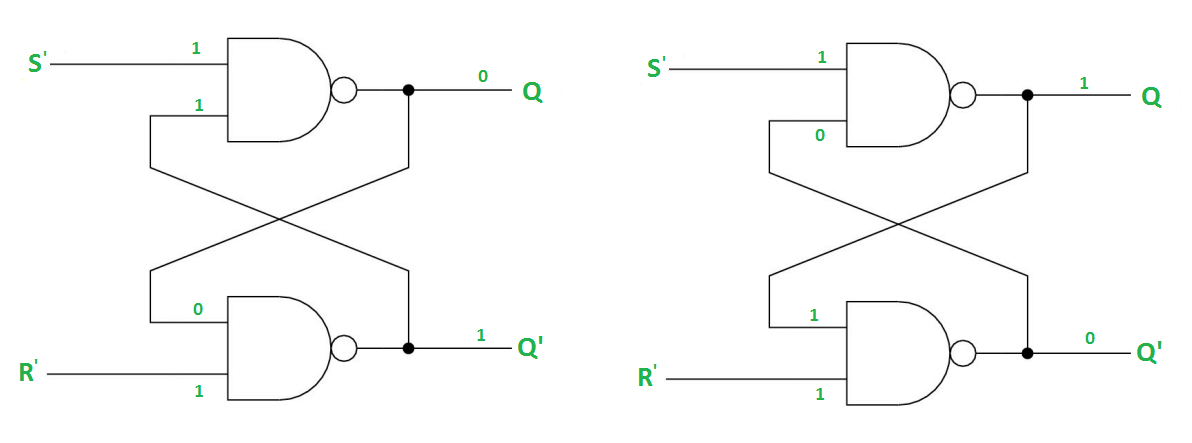

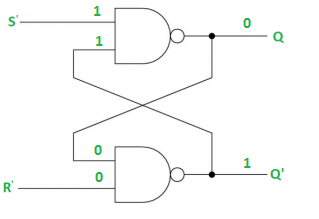

Caso-1: S’=R’=1 (S=R=0) –

Se Q = 1, gli ingressi Q e R’ della seconda porta NAND sono entrambi 1.

Se Q = 0, gli ingressi Q e R’ per il 2° gate NAND sono rispettivamente 0 e 1.

Caso-2: S’=0, R’=1 (S=1, R=0) –

Come S’=0, l’uscita del 1° gate NAND, Q = 1 (stato SET). Nel 2° cancello NAND, poiché gli ingressi Q e R’ sono 1, Q’=0.

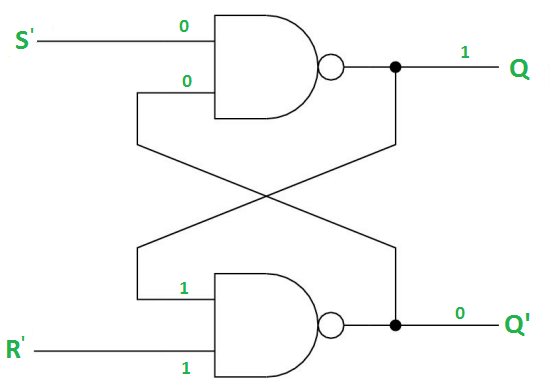

Caso-3: S’= 1, R’= 0 (S=0, R=1) –

Come R’=0, l’uscita del 2° cancello NAND, Q’ = 1. Nel 1° cancello NAND, poiché gli ingressi Q e S’ sono 1, Q=0 (stato RESET).

Caso-4: S’= R’= 0 (S=R=1) –

Quando S=R=1, sia Q che Q’ diventano 1 che non è permesso. Quindi, la condizione di ingresso è proibita.

Il Latch SR usando il NOR gate è mostrato qui sotto:

Gated SR Latch –

Un Gated SR latch è un latch SR con ingresso di abilitazione che funziona quando l’abilitazione è 1 e mantiene lo stato precedente quando l’abilitazione è 0.

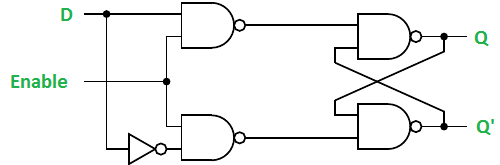

Gated D Latch –

Il latch D è simile al latch SR con alcune modifiche. Qui, gli ingressi sono complementari l’uno all’altro. Il progetto del D latch con segnale di abilitazione è dato qui sotto:

La tabella della verità per il D-Latch è mostrata qui sotto:

| Enable | D | Q(n) | Q(n+1) | STATE |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | Nessun cambiamento |

Come l’uscita è uguale all’ingresso D, D latch è chiamato anche Transparent Latch. Considerando la tabella della verità, l’equazione caratteristica per il latch D con ingresso di abilitazione può essere data come:

Q(n+1) = EN.D + EN'.Q(n)