Latches zijn elementaire opslagelementen die werken met signaalniveaus (in plaats van signaalovergangen). Latches die worden aangestuurd door een kloktransitie zijn flip-flops. Latches zijn niveau-gevoelige apparaten. Latches zijn nuttig voor het ontwerp van de asynchrone sequentiële schakeling.

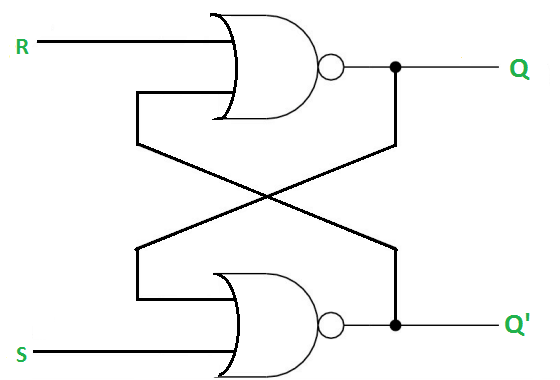

SR (Set-Reset) Latch – SR Latch is een schakeling met:

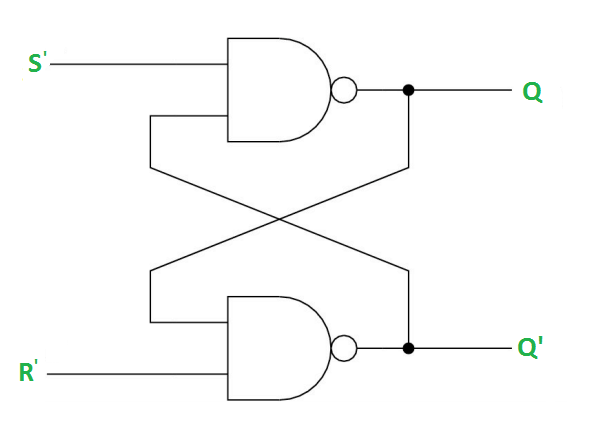

(i) 2 kruislings gekoppelde NOR-poorten of 2 kruislings gekoppelde NAND-poorten.

(ii) 2 ingangen S voor SET en R voor RESET.

(iii) 2 uitgangen Q, Q’.

| Q | Q’ | STATE |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

Onder normale omstandigheden, blijven beide ingangen 0. Hierna volgt de RS Latch met NAND-poorten:

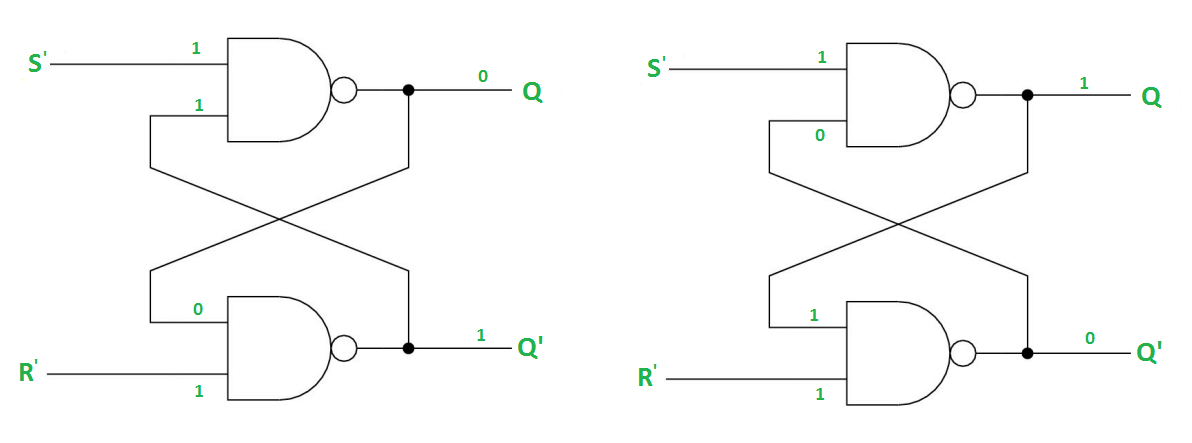

Geval-1: S’=R’=1 (S=R=0) –

Als Q = 1, zijn Q- en R’-ingangen voor de 2e NAND-poort beide 1.

Als Q = 0, zijn Q- en R’-ingangen voor 2e NAND-poort respectievelijk 0 en 1.

Case-2: S’=0, R’=1 (S=1, R=0) –

Als S’=0, is de uitgang van de 1e NAND-poort, Q = 1 (SET-toestand). In de tweede NAND-poort zijn de ingangen Q en R gelijk aan 1, zodat Q = 0.

Fase-3: S’= 1, R’= 0 (S=0, R=1) –

Als R’=0, is de uitgang van de tweede NAND-poort, Q’ = 1. In de 1e NAND-poort zijn de Q- en S’-ingangen 1, waardoor Q=0 (RESET-toestand)

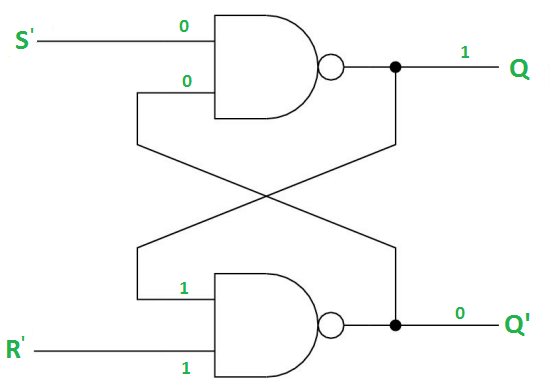

Case-4: S’= R’= 0 (S=R=1) –

Wanneer S=R=1, worden zowel Q als Q’ 1, wat niet is toegestaan. De ingangsvoorwaarde is dus verboden.

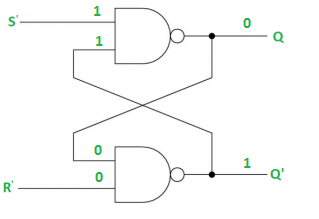

De SR-latch met behulp van de NOR-poort wordt hieronder getoond:

Gated SR-latch –

Een Gated SR-latch is een SR-latch met vrijgave-ingang die werkt als vrijgave 1 is en de vorige toestand behoudt als vrijgave 0 is.

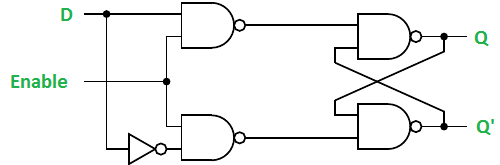

Gated D Latch –

D latch is vergelijkbaar met SR latch met enkele modificaties. Hier zijn de ingangen complementair aan elkaar. Het ontwerp van D-latch met Enable-signaal is hieronder gegeven:

De waarheidstabel voor de D-latch is hieronder weergegeven:

| Enable | D | Q(n) | Q(n+1) | STATE |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | No Change |

Zoals de uitgang gelijk is aan de ingang D, wordt D latch ook wel Transparent Latch genoemd. Op basis van de waarheidstabel kan de karakteristieke vergelijking voor D latch met vrijgave-ingang als volgt worden gegeven:

Q(n+1) = EN.D + EN'.Q(n)