Latches sind grundlegende Speicherelemente, die mit Signalpegeln (und nicht mit Signalübergängen) arbeiten. Latches, die durch einen Taktübergang gesteuert werden, sind Flipflops. Latches sind pegelabhängige Bauelemente. Latches sind für den Entwurf der asynchronen sequentiellen Schaltung nützlich.

SR (Set-Reset) Latch – SR Latch ist eine Schaltung mit:

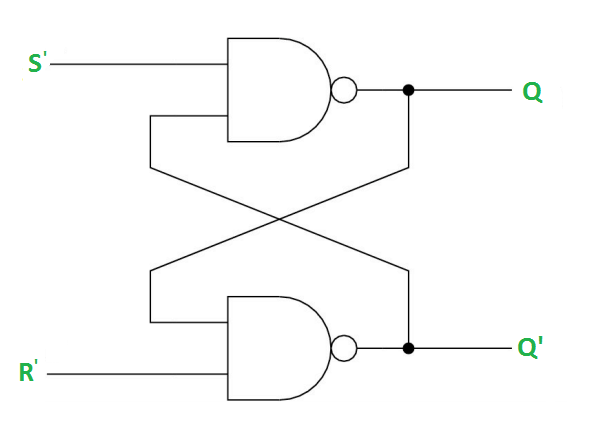

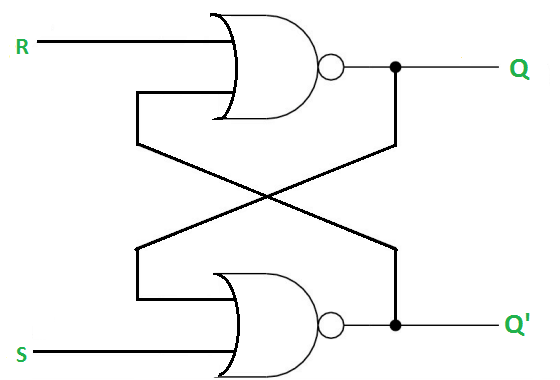

(i) 2 kreuzgekoppelten NOR Gatter oder 2 kreuzgekoppelten NAND Gatter.

(ii) 2 Eingänge S für SET und R für RESET.

(iii) 2 Ausgänge Q, Q‘.

| Q | Q‘ | ZUSTAND |

|---|---|---|

| 1 | 0 | Set |

| 0 | 1 | Reset |

Unter normalen Bedingungen, bleiben beide Eingänge auf 0. Nachfolgend das RS-Latch mit NAND-Gattern:

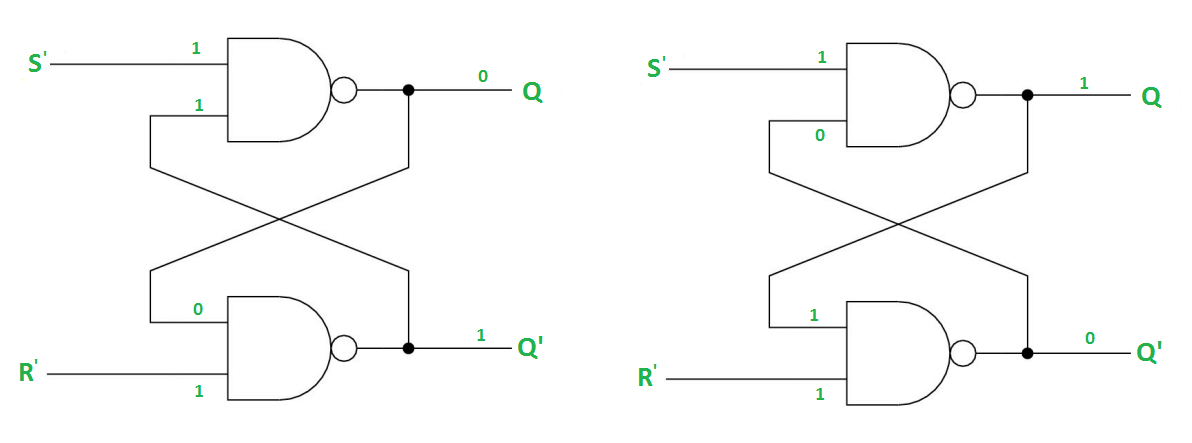

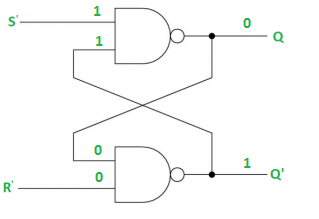

Fall-1: S’=R’=1 (S=R=0) –

Wenn Q = 1, sind die Eingänge Q und R‘ für das 2. NAND-Gatter beide 1.

Wenn Q = 0 ist, sind die Eingänge Q und R‘ des 2. NAND-Gatters 0 bzw. 1.

Fall-2: S’=0, R’=1 (S=1, R=0) –

Wenn S’=0 ist, ist der Ausgang des 1. NAND-Gatters, Q = 1 (SET-Zustand). Im 2. NAND-Gatter sind die Eingänge Q und R‘ gleich 1, Q’=0.

Fall 3: S’= 1, R’= 0 (S=0, R=1) –

Da R’=0, ist der Ausgang des 2. NAND-Gatters, Q‘ = 1. Im 1. NAND-Gatter sind die Eingänge Q und S‘ 1, Q=0 (RESET-Zustand).

Fall 4: S’= R’= 0 (S=R=1) –

Wenn S=R=1 ist, werden sowohl Q als auch Q‘ 1, was nicht erlaubt ist. Also ist die Eingabebedingung verboten.

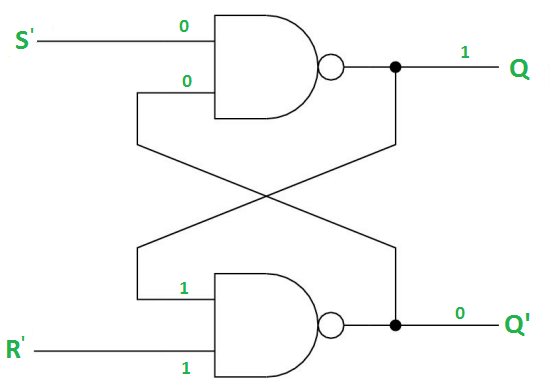

Das SR-Latch mit NOR-Gatter ist unten dargestellt:

Gated SR Latch –

Ein Gated SR Latch ist ein SR-Latch mit Enable-Eingang, das funktioniert, wenn Enable 1 ist und den vorherigen Zustand beibehält, wenn Enable 0 ist.

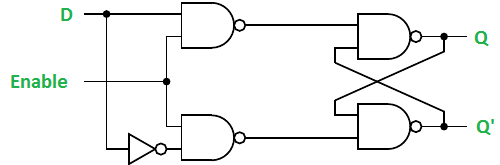

Gated D Latch –

D Latch ist ähnlich wie SR Latch mit einigen Änderungen. Hier sind die Eingänge komplementär zueinander. Der Entwurf eines D-Latch mit Enable-Signal ist unten angegeben:

Die Wahrheitstabelle für das D-Latch ist unten dargestellt:

| Enable | D | Q(n) | Q(n+1) | STATE |

|---|---|---|---|---|

| 1 | 0 | x | 0 | RESET |

| 1 | 1 | x | 1 | SET |

| 0 | x | x | Q(n) | Keine Änderung |

Da der Ausgang gleich dem Eingang D ist, wird D-Latch auch als Transparent Latch bezeichnet. Unter Berücksichtigung der Wahrheitstabelle kann die charakteristische Gleichung für D-Latch mit Freigabeeingang wie folgt angegeben werden:

Q(n+1) = EN.D + EN'.Q(n)